-

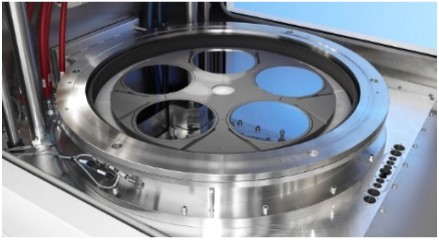

MOCVD

英诺赛科正在使用最新一代的 Aixtron MOCVD reactor G5+C™ 来生产8英寸GaN-on-Si晶圆。

-

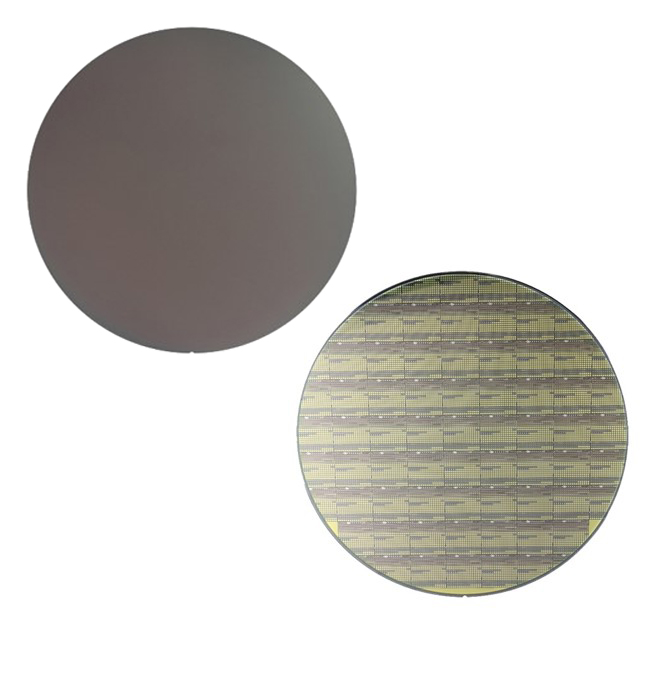

8英寸 GaN-on-Si epi-buffer

英诺赛科开发了专为优化高压(HV)和低压(LV)器件的8英寸GaN-on-Si外延缓冲技术。

通过内部控制外延技术,英诺赛科可以快速调整外延制程,以适应特定的需求或应用。

英诺赛科不断努力在技术、性能和产能方面进一步优化,以确保高性价比的GaN-on-Si技术。

-

外延

Innoscience已经成功地生产超过数万片8英寸硅基氮化镓晶圆,每个月高压和低压器件均能稳定量产出货。

同时,优化了GaN-on-Si外延工艺,获得了均匀、无裂纹、低位错密度和低缺陷的外延晶圆。

-

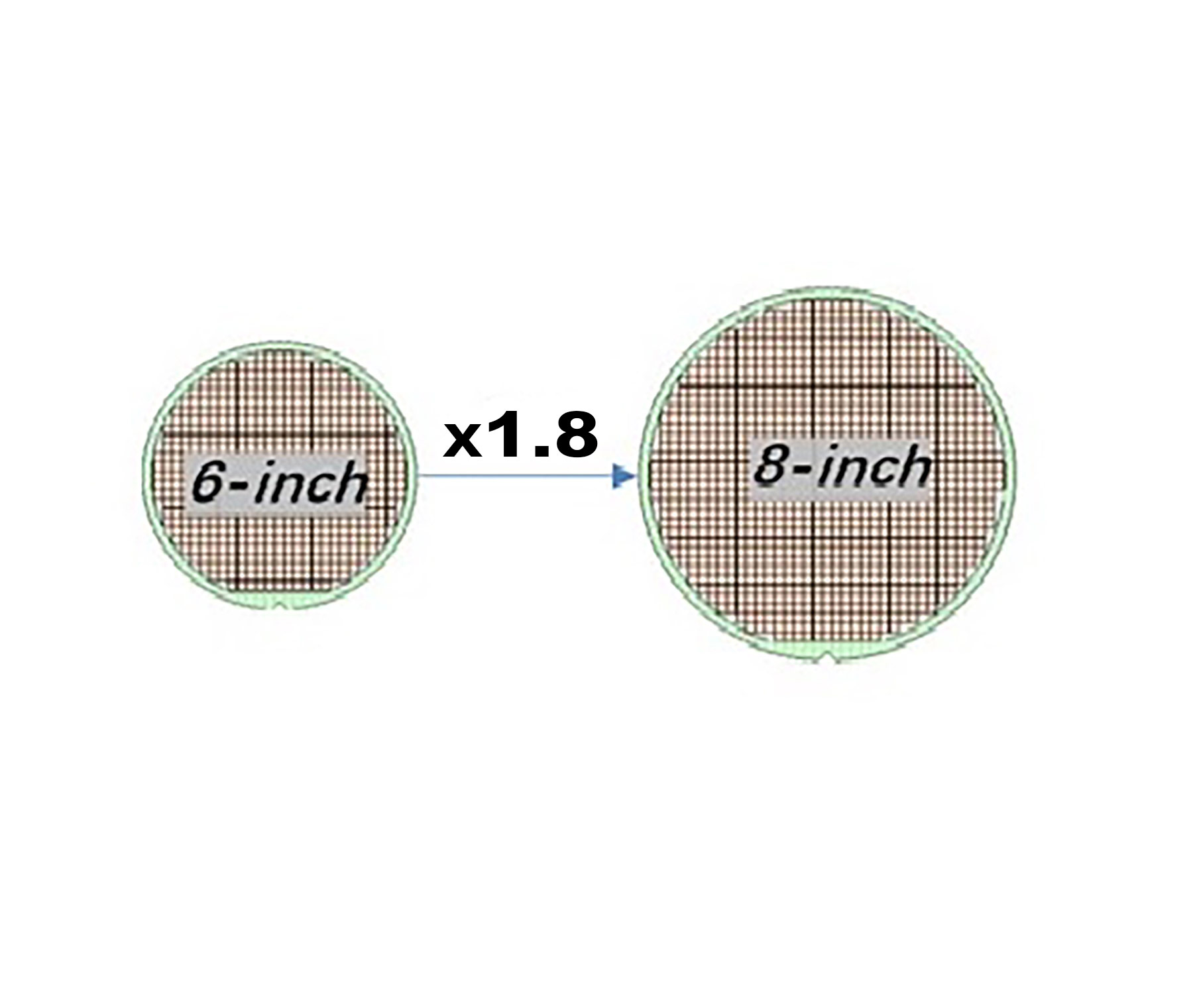

8英寸GaN-on-Si晶圆片

在过去的40年里,晶圆尺寸一直在不断扩大,从6英寸到8英寸,再到今天的12英寸。其目的都是在于同时在晶圆上获得更多的器件,从而降低成本。

同样,其他氮化镓厂商目前的晶圆尺寸仍为4英寸或6英寸,而英诺赛科从一开始就战略性地采用8英寸的晶圆尺寸。英诺赛科所生产的8英寸GaN-on-Si晶圆,其每片晶圆的器件数量比6英寸晶圆多80%,这对器件成本有直接的影响。

-

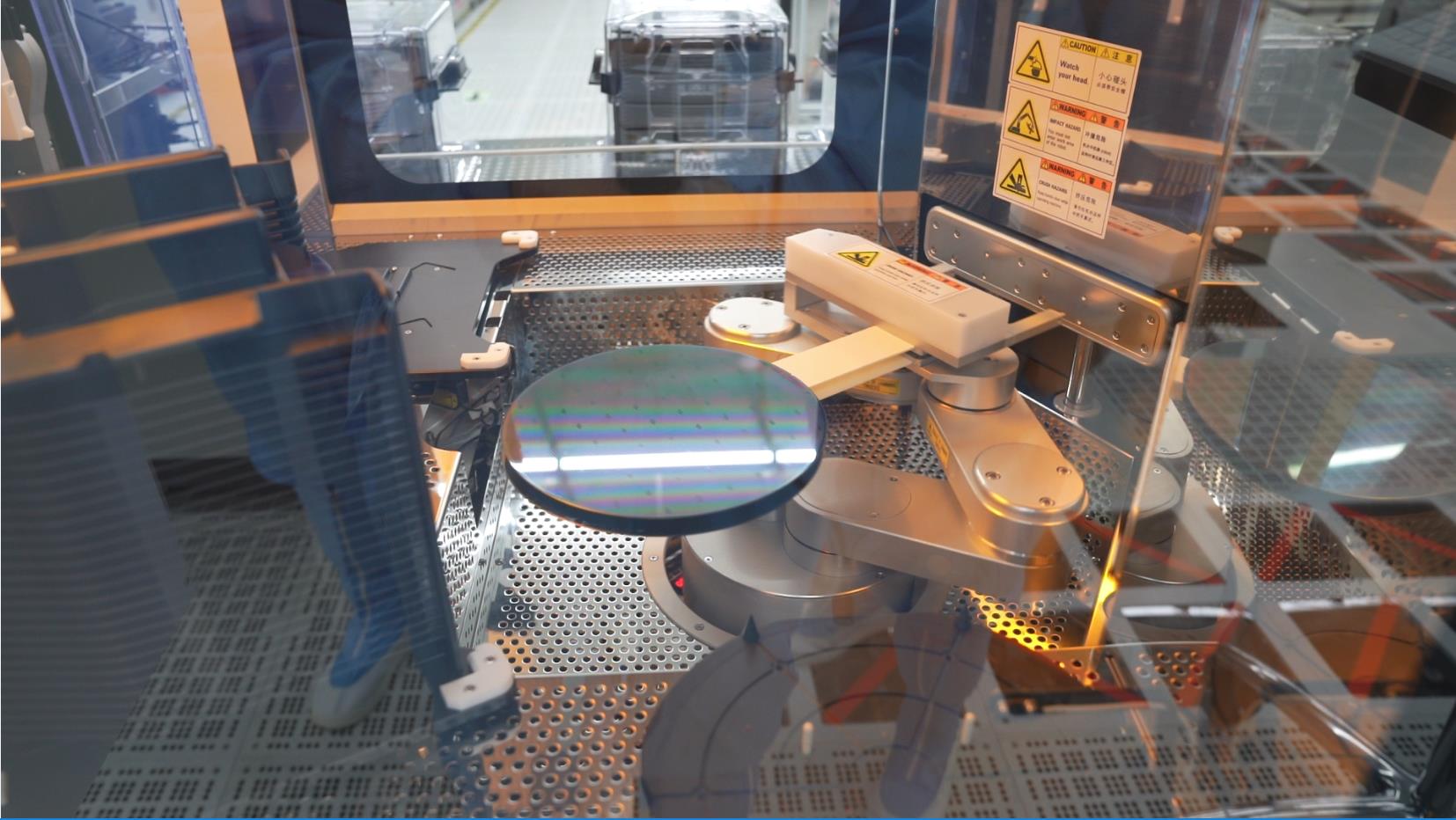

高通量硅兼容的制造工艺

硅技术的大规模生产已经有40年了。在设备制造商的支持下,硅器件制造商在产能和质量方面优化了他们的工艺,以便利用每一英寸硅片,并用他们的生产线生产尽可能多的晶圆片。

因此,英诺赛科决定在生产线上配备全新的8英寸制造设备(如ASML光刻机),并开发一个与硅兼容的工艺流程(如无金工艺、平整工艺、蚀刻工艺等)。

英诺赛科利用多年的经验,生产成本低、效益高的8英寸氮化镓器件。

-

高良率

如果工艺良率没有得到优化,晶圆的利用率就不高。

由于英诺赛科采用集芯片设计、外延生长、芯片制造、测试与失效分析于一体的IDM全产业链模式,因此控制整个制造流程(从外延到晶体管完成),英诺赛科可以改进每个技术方面,以获得晶圆和器件高良率。

英诺赛科优化了外延工艺,以获得均匀、可重复和坚固的8英寸GaN-on-Si外延片,这是器件加工的基础。此外,英诺赛科还优化了工艺技术,扩大了工艺窗口等,以此来获得可大规模量产的工艺及更高晶圆的利用率。

-

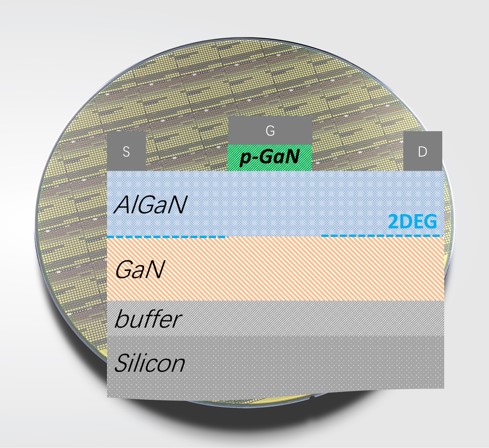

E-mode/常关mode

功率半导体市场需要常关的器件,这意味着当晶体管的栅极设置为0V时,没有电流传导。

GaN HEMT(高电子迁移率晶体管)的自然形式是常开或称为耗尽型(D-mode),这需要特殊的驱动器或放置在一个共源共栅封装解决方案来实现常关操作。

英诺赛科GaN HEMT本质上是常关或称为增强型(E-mode)器件。通过在AlGaN势垒上生长p-GaN层,沉积并图形化栅极金属,然后选择性地在AlGaN势垒上使用p-GaN层来实现常关。

栅极金属层与p-GaN层形成(肖特基)接触,因此,平衡通道中的电势上升,从而实现常关模式。

-

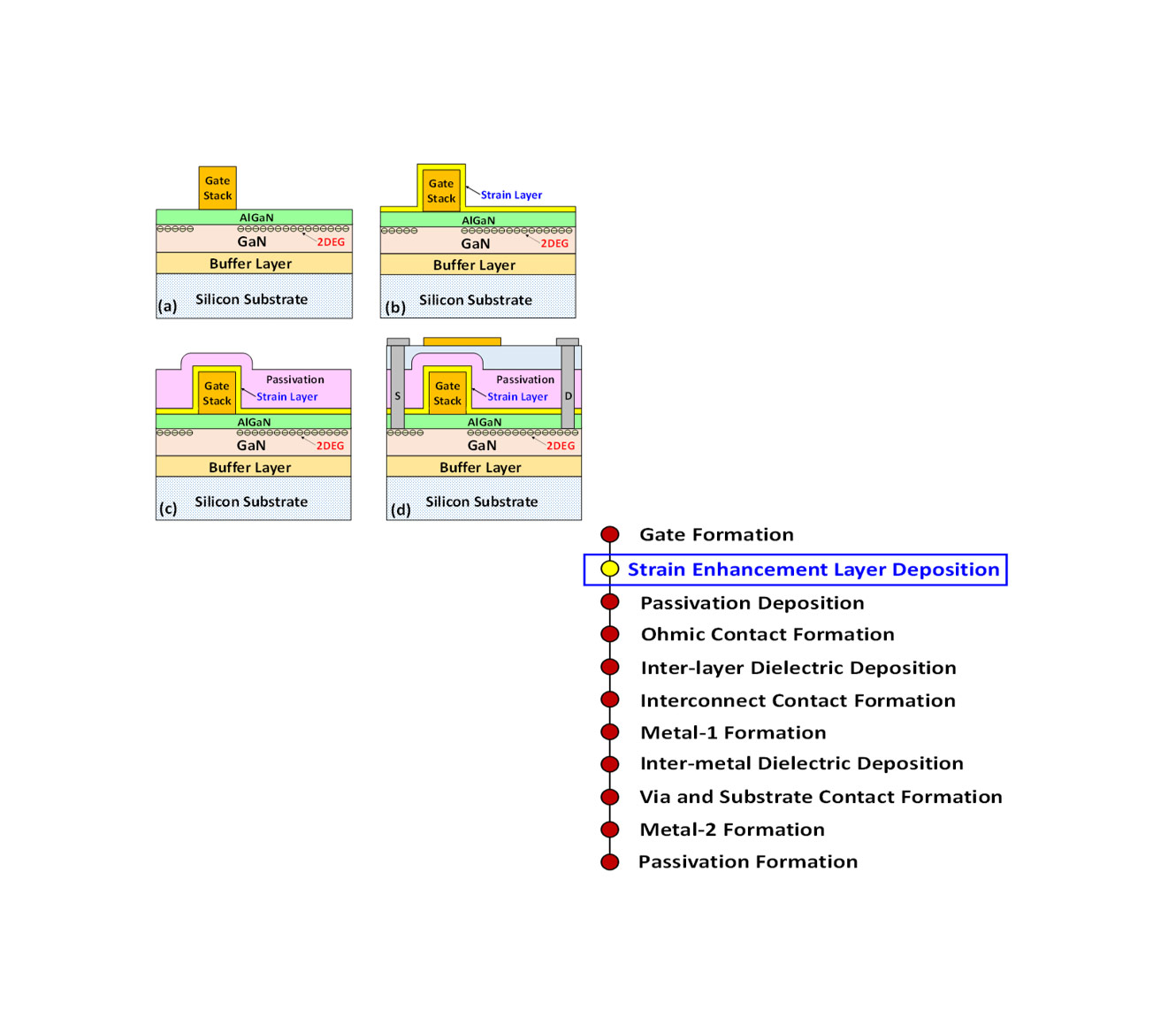

低特定RDS_ON

英诺赛科对GaN技术进行了优化,实现器件高性能、高可靠性、大规模生产和降低成本。定义技术性能的一个关键参数是特定的 RDS_ON ,单位面积的导通电阻(也就是说,对于给定的导通电阻,电阻RDS_ON越小,器件设计得越小; 器件越小,每片晶圆中可以放置的器件数量就越多,因此成本就越低)。

英诺赛科开发了一种应变增强层技术,它包括定义在栅极堆叠后沉积特定层。由应变增强层产生的应力会引起额外的压电极化,使得2DEG密度增加,因此与没有应变层的器件相比, RDS_ON降低了66%。

由于应变增强层是在栅极形成后沉积的,它只影响接入区域电阻,不影响阀值、泄漏等其他器件参数。

得益于这项技术,英诺赛科的GaN-on-Si E-mode HEMT具有非常低的特定导通电阻。

-

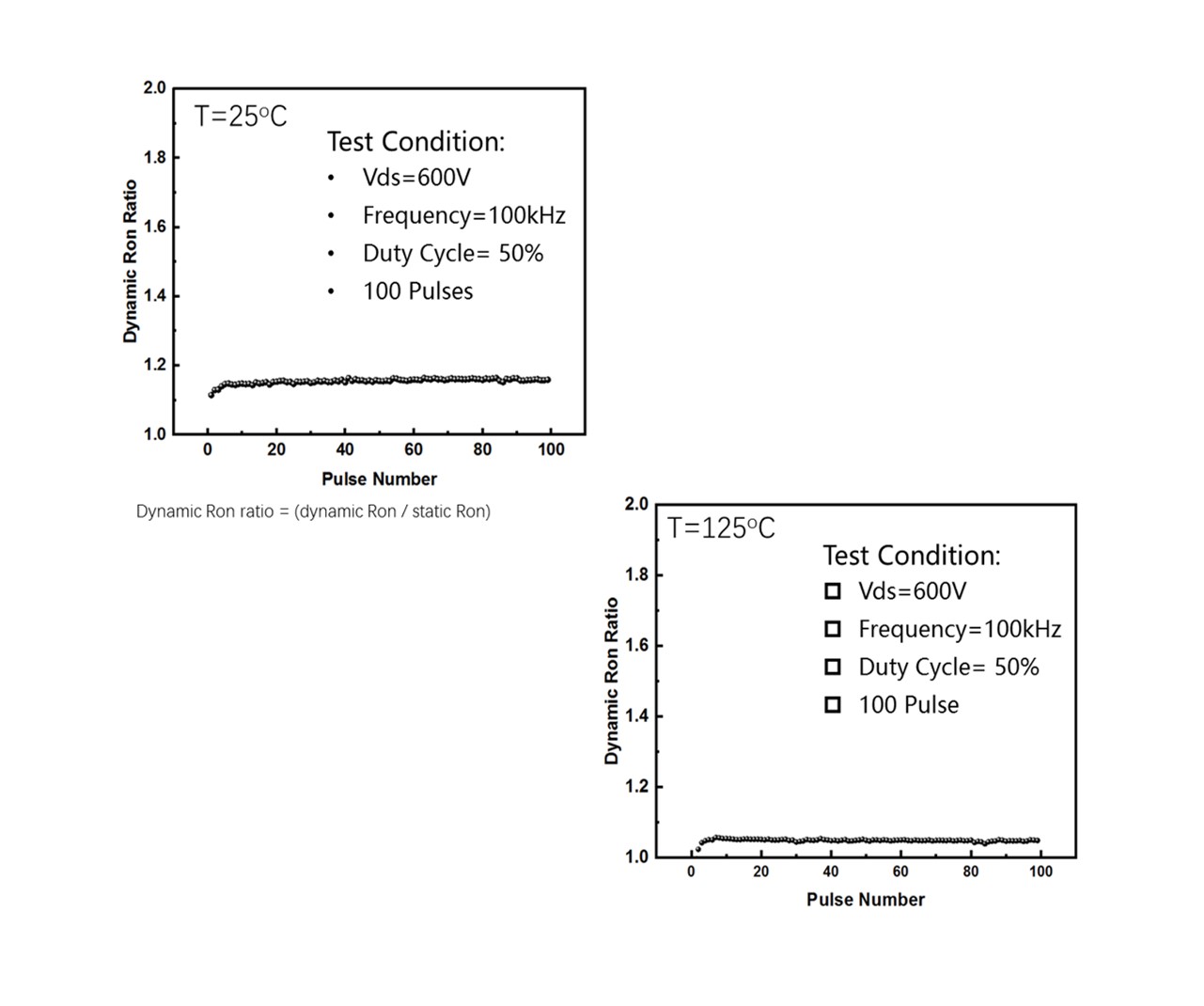

优秀的性能

英诺赛科 GaN技术在性能和可靠性方面进行了优化。

英诺赛科 GaN技术的关键技术之一是在整个温度和电压范围内极低的动态 RDS_ON 。这意味着在实际的功率开关应用中,器件的导通电阻不会增加。

没有经过优化的GaN技术,在器件关闭,高压作用于器件漏极时,通常会出现导通电阻漂移,就像器件在实际应用中所经历的那样。这不仅对整个系统的性能有害,因为更高的电阻意味着更高的损耗,而且对器件的可靠性也有害,因为器件变得更热,更容易发生故障。

这也是英诺赛科GaN技术在实际应用中表现出优异的温度稳定性而不会出现过热的原因之一。

英诺赛科通过精心优化外延和器件工艺技术实现了这一目标。

简体

简体

English

English